Stap 7: Ontwerp een prioriteit-Encoder

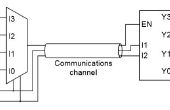

In dit gedeelte gaan we ontwerpen een encoder 4 vergende prioriteit. Vier ingebouwde schakelaars zal worden gebruikt als gegevens ingangen. Een ander schuifschakelaar zal fungeren als "Enable" signaal. Twee LEDs zal tonen de gecodeerde waarde van ingangen, en een andere twee LED's fungeren als de "GS" en het "Eout"-signaal.

Maak een project in Xilinx Vivado gericht op de FPGA-board die u, zoals in eerdere projecten gebruikt.

Maak een Verilog module genaamd encoder met ingangen ik Ein en uitgangen Y, Eout en GS als volgt:

(decoder_3_8) 1 module

2 input [3:0] I,

3 input Ein,

4 output [1:0] Y,

5 uitvoer GS,

6 uitgang Eout

7);

De meest efficiënte manier om te beschrijven van het gedrag van een encoder prioriteit is te gebruiken als-instructie in een altijd blokkeren. Zoals we hier drie uitgangen hebben, zullen we de gedrags beschrijving code voor die drie uitgangen in drie altijd blokkeert.

1 reg [1:0] Y;

2 reg GS;

3 reg Eout;

4

5 altijd @ (I, Ein)

6 beginnen

7 if(Ein == 1)

8 Y = (IK [3] == 1)? 2' d3: ()

9 (ik [2] == 1)? 2' d2: ()

10 (ik [1] == 1)? 2' d1: 2' d0

11)

12);

13 anders

14 Y = 2' d0;

15 einde

16

17 altijd @ (I, Ein)

18 beginnen

19 als (Ein == 1 & & ik == 0)

20 Eout = 1' b1;

21 anders

22 Eout = 1' b0;

23 einde

24

25 altijd @ (I, Ein)

26 beginnen

27 als (Ein == 1 & & ik! = 0)

28 GS = 1' b1;

29 anders

30 GS = 1' b0;

31 einde

Maak een XDC bestand en kaart:

-I [3:0] bij SW3 SW2, SW1, SW0

-Ein aan SW7

-Y [1:0] op LED 1-0

-Eout op LED 7

-GS LED 6