Stap 2: Ontwerp een Multiplexer

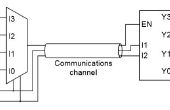

Dit project begint met het ontwerpen van een 4-1-2-bits bus multiplexer. Acht on-board dia schakelaars zal worden gebruikt om de gegevens ingangen, twee drukknoppen zal worden gebruikt als select signalen en LEDs 0 en 1 zal worden gebruikt om de output van de multiplexer. In plaats van uitvoering van de multiplexer met logica operatoren, we gaan beschrijven het circuit gedragsgestoorde met behulp van een altijd blok en een if-instructie of een case-statement.

Wij zijn drie manieren om te coderen de multiplexer gedragsgestoorde hier presenteren. Echter, u hoeft alleen een in uw code. U wordt aangemoedigd om uit alle drie van de verschillende manieren om te begrijpen en ervaar het verschil in de syntaxis van de Verilog te proberen.

Maak een project in Xilinx Vivado gericht op de FPGA-board die u gebruikt, zoals u hebt gedaan in de vorige labs.

Maak een Verilog-module genaamd mux_4_1 met ingangen I0, I1, I2, I3, Sel en output Y als volgt:

(mux_4_1) 1 module

2 ingang [1:0] I0,

3 input [1:0] I1,

4 input [1:0] I2,

5 ingang [1:0] I3,

6 input [1:0] Sel,

7 uitgang [1:0] Y

8);