EE214

Project 6: Een eenvoudige communicatiesysteem

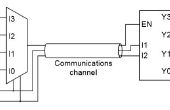

In dit project, zal u een 4-tegen-1 mux en een decoder met een signaal inschakelen als een "de-mux" om een eenvoudige seriële data zender ontwerpen. Mux zowel de-mux zal worden uitgevoerd in twee Verilog bestanden voor toekomstige hergebruik. Ee

Project 2.1: Uitvoering van een eenvoudige logica Circuit

In dit project downloadt u een bit bestand aan uw Raad van bestuur om de FPGA configureren met vier verschillende logische circuits. De circuits gebruiken knoppen en schakelaars voor ingangen en LEDs voor uitgangen. U moet de logische circuits sonde

Project 3.1: Meerderheid van 5

Hoe kon u vinden een meerderheid van de stemmen als elk van de vijf kiezers heeft een schakelaar om te stemmen voor Ja of Nee? De logica is vrij eenvoudig en zal worden gebruikt in dit project. Elk moment zijn er drie of meer van de vijf die stemming

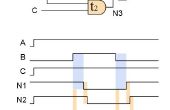

Project 7: Simuleren Glitch en vertraging bij de combinatorische Circuits

In dit project gaan we onderzoeken de vertragingbij combinatorische circuits. We gaan om te vertellen van de simulator van de vertraging van elke poort in Verilog en simuleren van de circuits om te zien hoe de vertraging kan invloed hebben op het ged

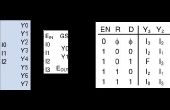

Project 5: Multiplexer, Decoder, Encoder en Shifter

In dit project zal u een multiplexer, een decoder, een coderingsprogramma en een shifter met behulp van Verilog HDL ontwerpen. In plaats van het opbouwen van het circuit logica operators gebruiken, leert u om te beschrijven een circuit gedragsgestoor